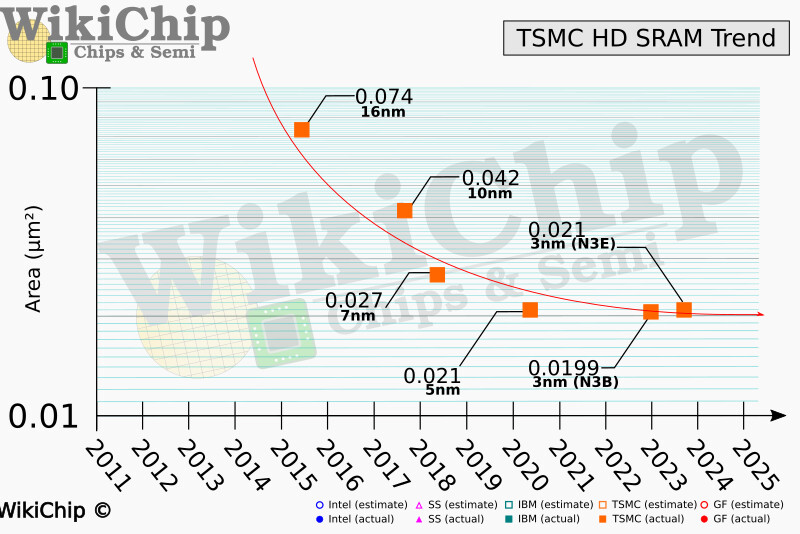

Когда TSMC анонсировала 3 нм техпроцесс специалисты компании говорила только о возможности логического масштабирования двух новых этапов производства полупроводников в дальнейшем. И оказывается, что для таких разговоров была причина, поскольку ресурс WikiChip подтверждает, что битовые ячейки SRAM, производящиеся по 3 нм техпроцессу, почти идентичны 5 нм битовым ячейкам SRAM. На технологическом симпозиуме 2023 компания TSMC представила дополнительную информацию о своей линейке 3 нм техпроцессов, включая логику и плотность SRAM.

Во-первых, техпроцесс 3 нм — это семейство техпроцессов TSMC «3 нм», которое имеет два направления: базовый техпроцесс N3B и Enhanced N3 (N3E). Базовый N3B использует новую (для TSMC) схему самовыравнивающихся контактов (SAC), которую Intel представила еще в 2011 году во времена 22 нм техпроцесса, что повышает производительность узла.

Несмотря на улучшение логической плотности N3 по сравнению с N5 «последнего поколения», плотность SRAM практически идентична. Первоначально TSMC утверждала, что плотность N3B SRAM была в 1,2 раза выше, чем у N5. Однако недавняя информация показывает, что фактическая плотность SRAM составляет всего 5%. Поскольку SRAM занимает большую часть транзистора и бюджета процессора, из-за чего растущие производственные затраты на использование N3B труднее оправдать, ведь улучшений почти нет. Соответственно улучшать производственные линии в дальнейшем также будет очень трудно и дорого, так что да, производители чипов постепенно упираются в стену.