В полупроводниковой индустрии грядут большие перемены. Как сообщают источники, мировой лидер в производстве чипов, компания TSMC, готовится к переходу от своей передовой технологии упаковки CoWoS к новому, ещё более перспективному подходу под названием CoPoS. Этот шаг может стать настоящей революцией в создании чипов для систем искусственного интеллекта и высокопроизводительных вычислений.

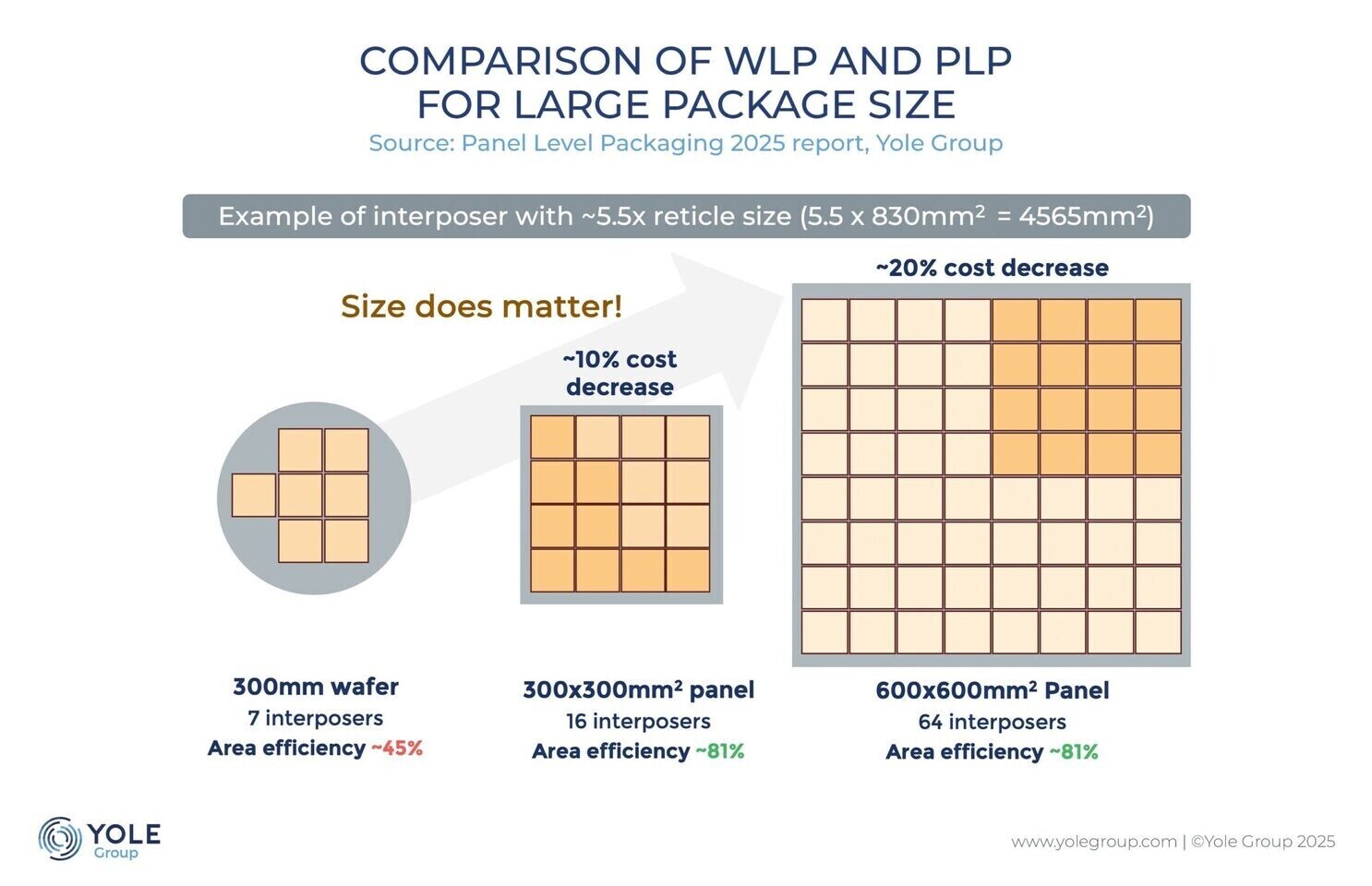

CoPoS (Chip-on-Panel-on-Substrate) — это новый метод, который, по сути, объединяет идеи CoWoS с технологией панельной упаковки. Вместо привычных круглых кремниевых подложек диаметром 300 мм TSMC планирует использовать большие квадратные и прямоугольные панели, что значительно увеличит площадь для размещения компонентов. Первые прототипы панелей будут иметь размеры около 310 × 310 мм, а в будущем компания намерена использовать панели размером до 750 × 620 мм. Это позволит размещать на одном кристалле больше ядер и чипов памяти HBM, а также уменьшить бесполезную площадь по краям.

Переход на панели даст сразу несколько преимуществ. Во-первых, это значительно увеличит выход годных кристаллов и снизит себестоимость каждого упакованного ускорителя. Во-вторых, новый подход позволит избежать проблем с деформацией, которые часто возникают при производстве всё более крупных чипов. В-третьих, это даст возможность создавать более масштабные и сложные чипы, что критически важно для развития ИИ-ускорителей.

TSMC уже активно готовится к внедрению новой технологии. Пилотные линии планируется запустить уже в 2026 году, а к массовому производству CoPoS компания собирается приступить в период с конца 2028 по первую половину 2029 года. Работы будут вестись на кампусе AP7 Chiayi, а также на будущих заводах в Аризоне. Заказы на оборудование и оснастку уже размещены у таких гигантов, как KLA и Applied Materials, а также у множества тайваньских производителей, включая Innolux. Важно отметить, что TSMC не отказывается от CoWoS и будет продолжать поддерживать её в переходный период.