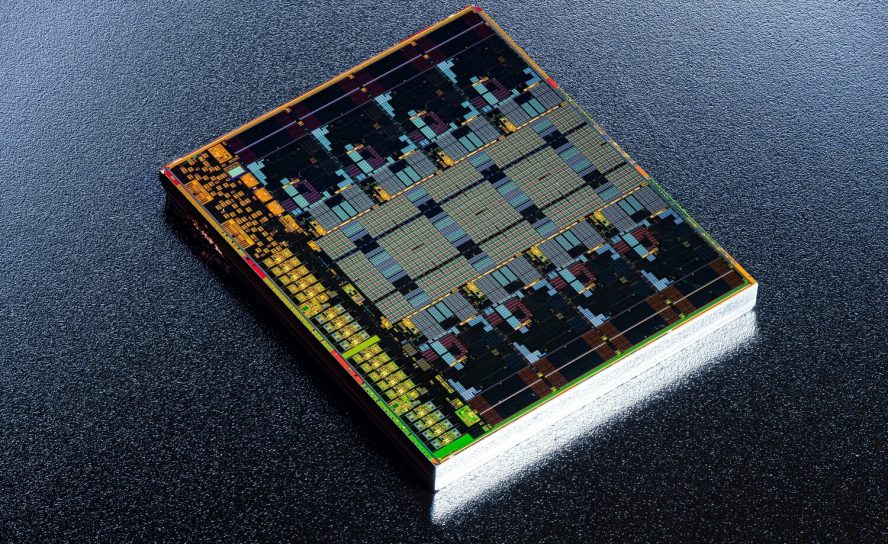

Были выпущены изображения кристаллов (die-shots) с высокой разрешающей способностью процессора AMD «Zen 5» с 8 ядрами CCD, и аннотированы Nemez, Fitzchens Fitz и HighYieldYT. Эти изображения предоставляют подробный обзор внешнего вида кремния и его различных компонентов, особенно нового ядра «Zen 5» с 512-битным FPU. Упаковка «Granite Ridge» выглядит аналогично «Raphael,» с возможностью наличия до двух кристаллов 8-ядерного процессора (CCD) в зависимости от модели процессора, и центрально расположенным кристаллом ввода/вывода (cIOD). Этот cIOD был перенесен из «Raphael,» что минимизирует затраты на разработку продукта для AMD, по крайней мере, для некорпусной части процессора. CCD «Zen 5» построен на техпроцессе TSMC N4P (4 нм).

В упаковке «Granite Ridge» расположение до двух «Zen 5» CCD значительно ближе друг к другу, чем «Zen 4» CCD на «Raphael.» На изображении выше можно увидеть площадку отсутствующего CCD за защитной маской стеклопластикового подложки, близко к присутствующему CCD. CCD содержит 8 полноразмерных ядер «Zen 5», каждое с 1 МБ кэша L2 и центрально расположенным 32 МБ кэшем L3, который разделяется всеми восемью ядрами. Единственные другие компоненты — это SMU (блок управления системой) и Infinity Fabric over Package (IFoP), которые соединяют CCD с cIOD.

Каждое ядро «Zen 5» физически больше, чем ядро «Zen 4» (построенное на процессе TSMC N5), из-за его 512-битной архитектуры обработки данных с плавающей запятой. Векторный движок ядра смещен к краю ядра. На CCD это должны быть края кристалла. FPU обычно является одним из самых горячих компонентов на ядре процессора, поэтому это имеет смысл. Самый внутренний компонент (обращенный к общему кэшу L3) — это 1 МБ кэша L2. AMD удвоила пропускную способность и ассоциативность этого 1 МБ кэша L2 по сравнению с кэшем на ядре «Zen 4.»

Центральная область ядра «Zen 5» включает в себя 32 КБ кэша L1I, 48 КБ кэша L1D, движок целочисленных вычислений и очень важную фронтальную часть процессора с Instruction Fetch & Decode, блоком Branch Prediction, кешом микрокоманд и планировщиком.

32 МБ кэша L3 на кристалле содержит ряды TSV (сквозные кремниевые vias), которые служат для стекаемых 3D V-cache. 64 МБ L3D (кристалл кэша L3) соединяется с кольцевой шиной CCD с помощью этих TSV, что делает 64 МБ 3D V-cache непрерывным с 32 МБ кэшем L3 на кристалле.

Наконец, кристалл ввода/вывода (cIOD). Здесь нет ничего нового, чип перенесен из «Raphael.» Он построен на техпроцессе TSMC N6 (6 нм). Почти треть площади кристалла занимает iGPU и его сопутствующие компоненты, такие как движок медиа-ускорения и движок отображения. iGPU основан на архитектуре графики RDNA 2 и имеет только один рабочий процессор (WGP), что соответствует двум вычислительным блокам (CU) или 128 потоковым процессорам. Другие ключевые компоненты на cIOD включают интерфейс PCIe Gen 5 с 28 линиями, два порта IFoP для CCD, довольно крупный SoC I/O, включающий USB 3.x и наследственную совместимость, а также очень важный контроллер DDR5 памяти с его двухканальным (четыре подсистемы) интерфейсом памяти.