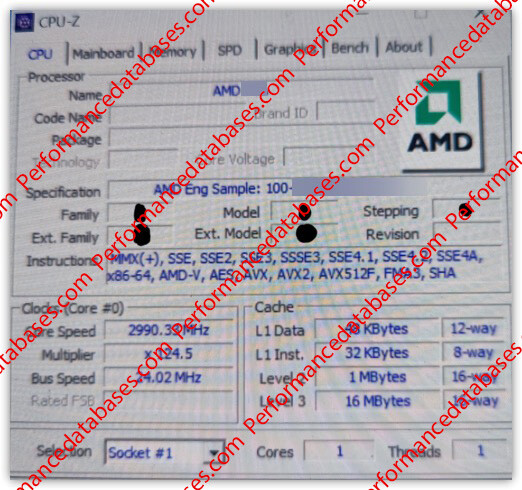

Опровергая предыдущие сообщения о том, что AMD увеличивает количество процессорных ядер в своих мобильных монолитных процессорах с нынешних 8-ядерных / 16-потоковых до 12-ядерных / 24-потоковых; мы узнаем, что процессор следующего поколения от компании под кодовым названием «Strix Point» фактически станет первым гибридным процессором компании. Ожидается, что чип будет оснащен двумя типами процессорных ядер, причем «Zen 5» будет микроархитектурой, отвечающей за производительность ядер, а «Zen 5c» — за эффективность ядер. Инженерный образец с 4 P-ядрами и 8 E-ядрами появился в Интернете благодаря Performancedatabases. На скриншоте HWiNFO показана конфигурация ядра инженерного образца из 4x P-ядер и 8x E-ядер с одинаковыми размерами кэша L1. С определением размера кэша L2 и кэша L3 возникают небольшие проблемы.

Из текущего дизайна ядра «Zen 4c» мы знаем, что это, по сути, уплотненная версия «Zen 4», предназначенная для чипов с более высокой плотностью, имеющих 16 ядер; и что он имеет те же ISA и IPC, что и «Zen 4», с той лишь разницей, что «Zen 4c» спроектирован с меньшим количеством совместно используемых кэшей L3 в их распоряжении, обычно сконфигурирован с более низкой тактовой частотой и имеет более высокую энергоэффективность, чем «Zen 4. «Площадь сердечников «Zen 4c» также на 35% меньше по площади матрицы, чем у «Zen 4». Компания могла бы разработать процессорные ядра «Zen 5c» с аналогичными целями проектирования.

Следовательно, кремниевый процессор «Strix Point» может иметь два CCX (комплекса процессорных ядер); один из которых имеет более крупные P-ядра «Zen 5» и определенный объем кэша L3, а другой CCX с меньшими ядрами «Zen 5c» и их собственными кэшами L3. По сути, он будет похож на «Renoir», в котором установлены два 4-ядерных CCXS с ядрами «Zen 2». Размеры кэша L1 для обоих типов ядер идентичны — 48 КБ L1D и 32 КБ L1I, и вполне вероятно, что оба типа ядер имеют по 1 МБ выделенного кэша L2 на ядро. Размеры кэша L3 могут варьироваться в зависимости от двух CCX, при этом размер P-core CCX составляет 16 МБ (4 МБ на ядро), а E-core CCX — 8 МБ (512 КБ на ядро).

Было бы интересно представить, как AMD справляется с гибридной архитектурой с точки зрения программного обеспечения. Intel использует Thread Director, аппаратное решение, предназначенное для передачи вычислительной нагрузки нужного типа на нужное ядро процессора. AMD может либо попытаться разработать собственную версию Thread Director, либо использовать менее сложное решение на базе операционной системы, например, то, что она делает со своими клиентскими процессорами с несколькими ПЗС-матрицами.