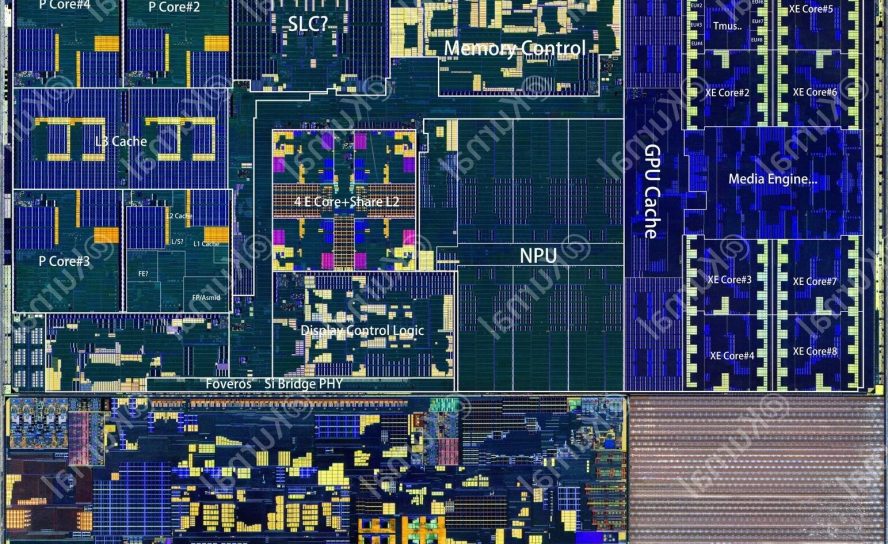

Некоторые из первых снимков кристаллов и аннотаций процессора Intel Core Ultra 200V «Lunar Lake» появились в сети благодаря снимкам от GeenWens и Kurnalsalts в Twitter. Не забудьте ознакомиться с нашей статьей Lunar Lake Technical Deep-dive, чтобы узнать основное о том, чем Lunar Lake отличается от «Meteor Lake.» Оба являются разнесенными процессорами на основе чиплетов, но Lunar Lake немного переосмысливает структуру. Все логические блоки процессора — ЦПУ, iGPU и NPU — расположены в центральном Compute tile, который построен по технологии TSMC 3 нм, в то время как все контроллеры ввода-вывода выведены на Platform Controller tile, построенный по технологии TSMC 6 нм, которые располагаются на базовом Foveros tile, действующем как интерпозитор, что облегчает высокоплотные микроскопические соединения между двумя тайлами. Базовый тайл располагается на стеклотекстолітном подложке, на которой также есть встроенная память LPDDR5X объемом 16 ГБ или 32 ГБ.

Аннотация от Kurnalsalts дает хорошее представление о Compute tile. Самый яркий аспект — это ЦПУ. «Lunar Lake» оснащён гибридным ЦПУ с четырьмя производительными и четырьмя энергоэффективными ядрами (4P+4E), однако два типа ядер не делят последний кэш, как в случае с Compute tile «Meteor Lake.» Четыре производительных ядра «Lion Cove» имеют по 2,5 МБ выделенного кэша L2 и делят 12 МБ кэша L3. Четыре энергоэффективных ядра «Skymont» не являются частью кольцевой шины, соединяющей четыре производительных ядра, их физически разделяют, как в случае с низкопотребляющими островами E-ядр на «Meteor Lake.» Кластер E-ядр делит 4 МБ кэша L2 между четырьмя E-ядрами. Этот кластер E-ядр напрямую подключен к переключающей сети Compute tile.

Контроллер памяти и PHY физически меньше, чем в «Meteor Lake,» поскольку он поддерживает только один тип памяти — LPDDR5X. PHY дополнен 8 МБ кэш-памяти, которую Intel называет кэшем на стороне памяти.

NPU занимает довольно большую часть центральной области Compute tile. Можно различить его шесть NCE (нейронных вычислительных движков), централизованный глобальный контроль и расширяемую ОЗУ. Рядом находится Xe2 «Battlemage» iGPU, который вместе со своими компонентами контроллера дисплея и мультимедиа занимает почти треть площади кристалла Compute tile. У него есть 8 ядер Xe2 и большой объем L2 кэш-памяти, который является эксклюзивным для iGPU. Рядом с контроллерами дисплея располагается Foveros bridge, через который Compute tile отправляет высокоплотные микроскопические соединения на PCH tile через базовый тайл.

6-нм Platform Controller tile не аннотирован, но по сути включает в себя контроллеры USB, дисплейный PHY, корневой комплекс PCIe и различные другие платформенные I/O.