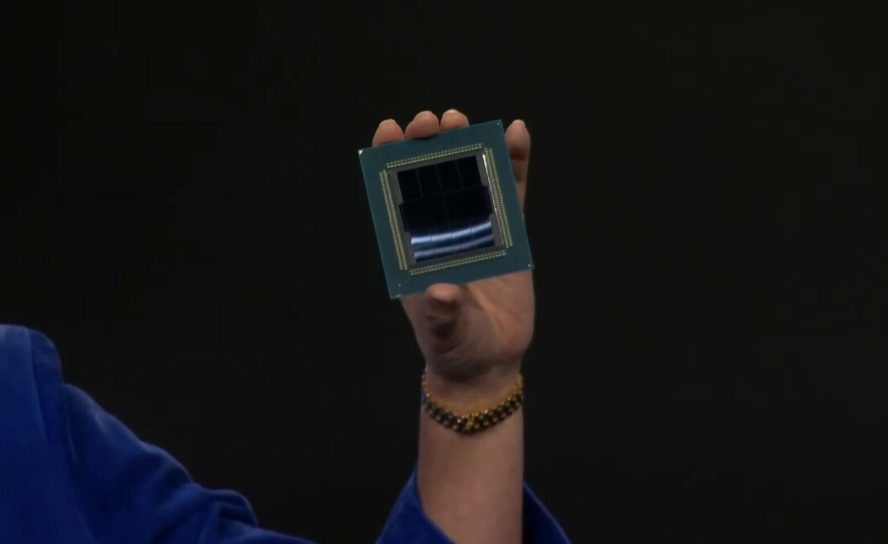

Генеральный директор AMD Лиза Су в рамках выставки CES 2026 впервые публично продемонстрировала серверный процессор нового поколения EPYC с кодовым именем Venice, который станет основой корпоративных ИИ-стоек Helios, запланированных к выходу в 2026 году. Новая платформа ориентирована на масштабные вычисления в области искусственного интеллекта и высокопроизводительных дата-центров, где ключевую роль играют связки из мощных CPU и специализированных GPU-ускорителей.

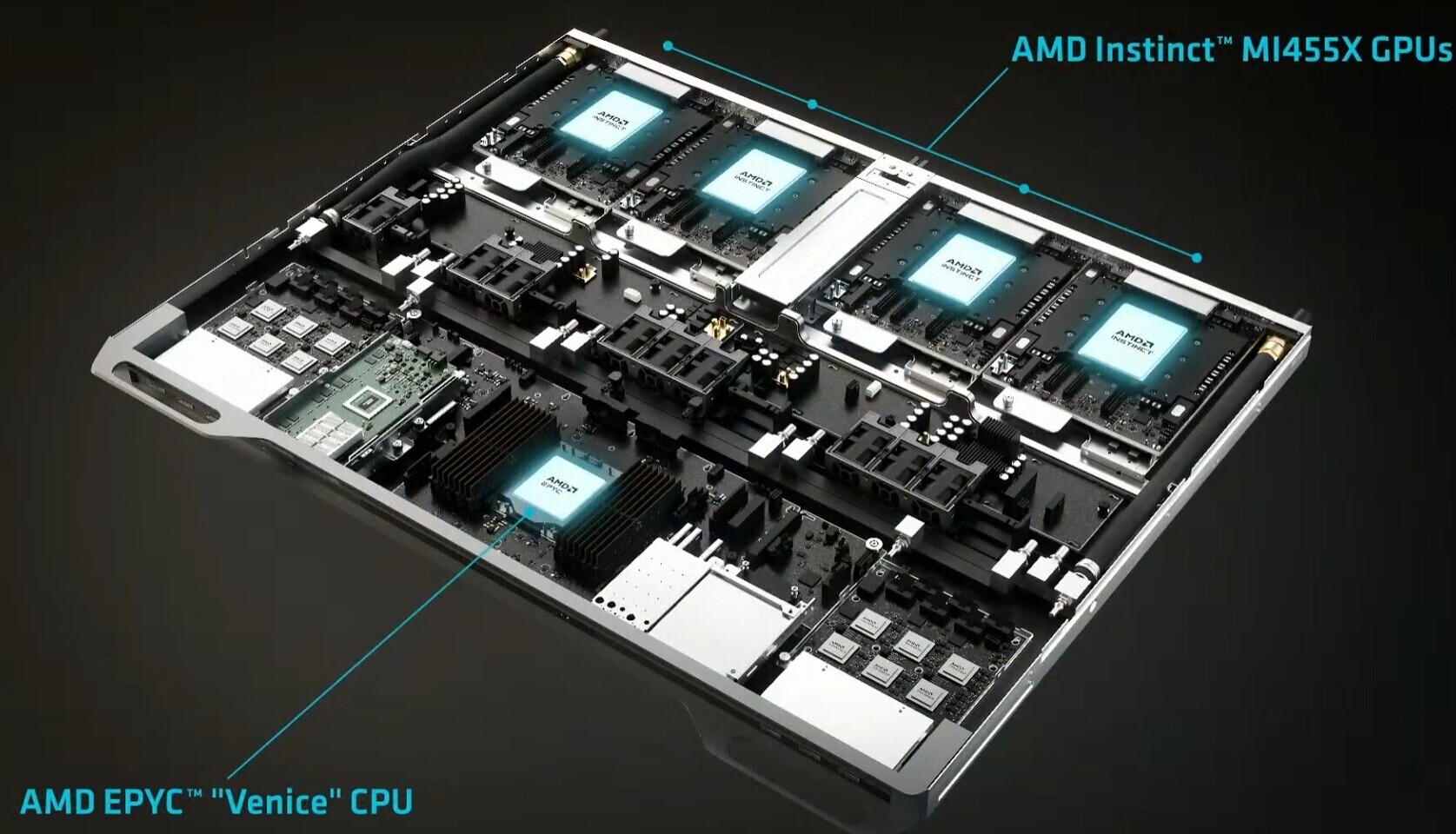

В конфигурации Helios каждый вычислительный узел объединяет сразу четыре графических ускорителя AMD MI455X и один процессор EPYC Venice с впечатляющей конфигурацией из 256 ядер и 512 потоков. Архитектура самого процессора заметно отличается от актуальных решений EPYC. AMD применила новую компоновку чиплетов, в которой используются два компактных серверных I/O-кристалла, выполненных по 4-нм техпроцессу и размещённых в центральной части корпуса. По обе стороны от них располагаются до восьми вычислительных чиплетов, каждый из которых производится по 2-нм нормам и содержит по 32 ядра архитектуры Zen 6.

Пока компания не раскрывает, идут ли речь о полноценных ядрах Zen 6, рассчитанных на высокие тактовые частоты, или об энергоэффективных вариантах Zen 6c с тем же набором инструкций и уровнем IPC, но более низкими частотами. В любом случае суммарная плотность вычислительных ресурсов выводит Venice в новый класс серверных процессоров, ориентированных прежде всего на задачи ИИ и обработки больших массивов данных.

Процессор оснащается 16-канальным контроллером памяти DDR5, который фактически представлен 32 субканалами. Именно это, по всей видимости, и стало причиной разделения серверного I/O-кристалла на два отдельных чипа, соединённых между собой высокоскоростной коммутационной фабрикой. Такой подход позволяет масштабировать пропускную способность памяти и повысить общую эффективность работы системы при экстремальных нагрузках.

Ожидается, что EPYC Venice также получит заметно увеличенное количество линий PCI Express и CXL по сравнению с текущим поколением. Это необходимо для одновременного подключения нескольких ИИ-ускорителей, специализированных DPU и сетевых адаптеров класса 800G, которые становятся стандартом для современных ИИ-кластеров. В совокупности эти изменения подчёркивают стратегию AMD по созданию глубоко интегрированных платформ для искусственного интеллекта, где CPU, GPU и высокоскоростные интерфейсы проектируются как единое целое.