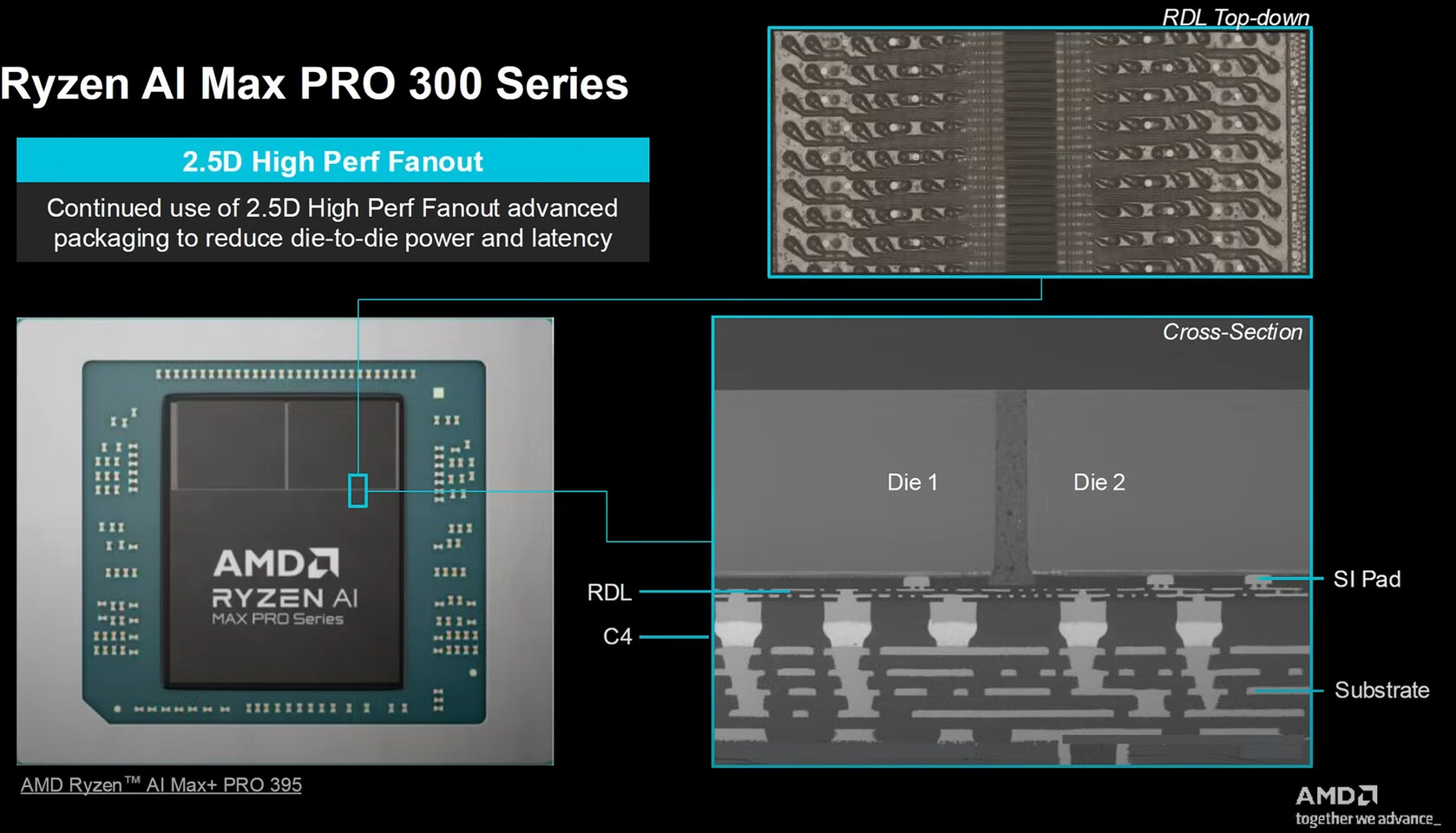

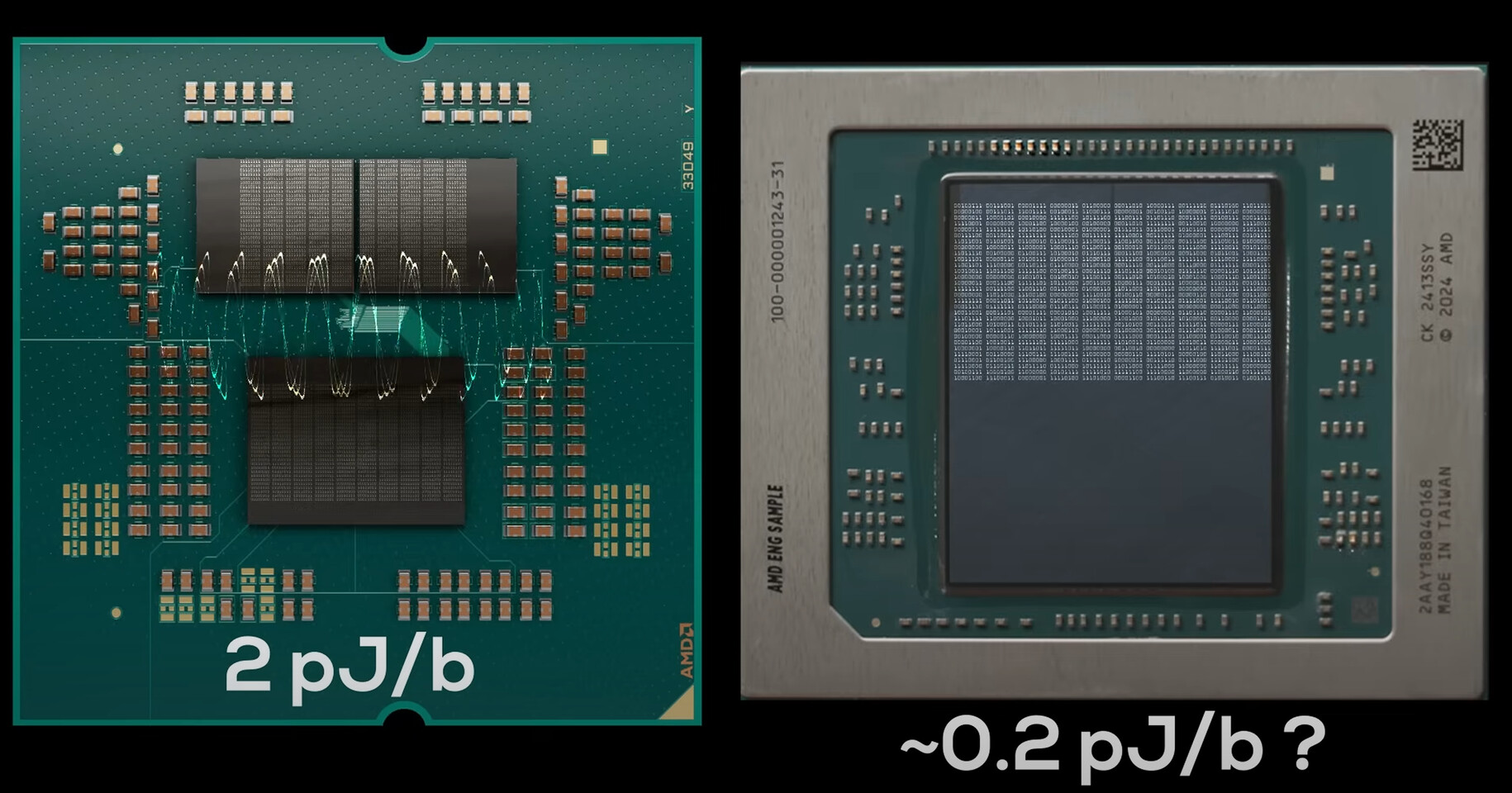

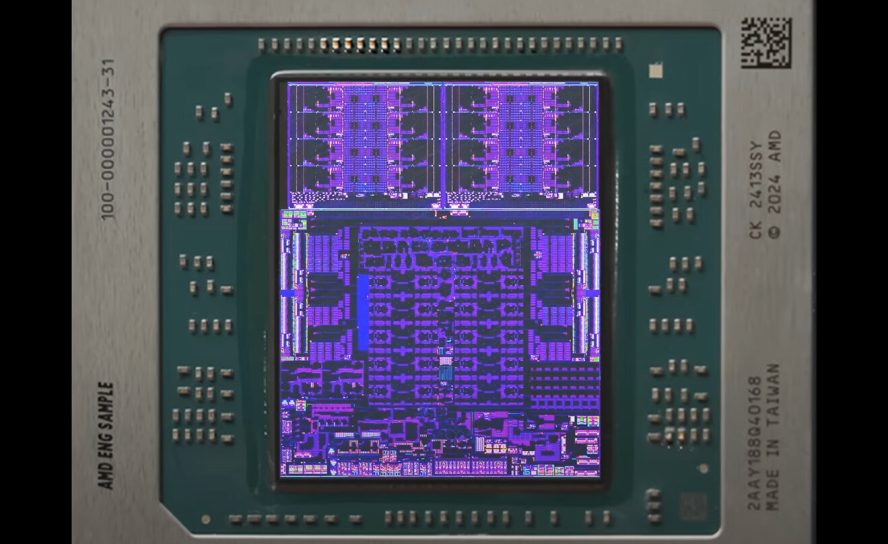

Согласно сообщениям от YouTube-канала High Yield, компания AMD, по всей видимости, переходит от традиционных SERDES-линков к широкому параллельному соединению типа «море проводов» (sea-of-wires). Эти связи будут прокладываться через передовую технологию упаковки с использованием Fan-Out и RDL (Re-Distribution Layer). Первые намеки на этот фундаментальный сдвиг в архитектуре были замечены на фотографиях готовящегося гибридного процессора Strix Halo APU.

Представленные образцы чипов демонстрируют прямоугольную площадку контактов там, где ожидалось Fan-Out-соединение, при этом заметно отсутствует крупный блок SERDES (сериализатор/десериализатор), который традиционно располагался по краям кристаллов (CCD). Этот паттерн, наряду с выбором упаковки, соответствующим технологии TSMC InFO-oS, предполагает, что AMD экспериментирует с плотными параллельными трассами. Это позволит каналам межкристальной фабрики пересекать подложку без необходимости преобразования в отдельные высокоскоростные последовательные линки.

Традиционная сериализация и десериализация данных на границе каждого кристалла требует дополнительной мощности и увеличивает задержку из-за восстановления тактового сигнала, эквализации, а также накладных расходов на кодирование и декодирование. Переходя к множеству коротких параллельных проводов, AMD может устранить повторную работу PHY-блоков и сократить задержки кругового пути. Кроме того, такой подход освобождает площадь, ранее занятую большими блоками SERDES, что позволяет ядрам (CCDs), контроллерам памяти и ускорителям располагаться ближе друг к другу, существенно снижая стоимость коммуникации.

Однако этот технический переход не лишен сложностей. Размещение множества параллельных трасс под кристаллом ставит серьезные проблемы, связанные с целостностью сигнала, тепловыделением, маршрутизацией и производством. Успех этого подхода критически зависит от многослойного дизайна RDL и тесного инженерного сотрудничества между командами, работающими над дизайном кристалла и упаковкой. Если AMD сможет успешно решить эти задачи и перенести данную архитектуру в поколение Zen 6, пользователи могут ожидать реального улучшения соотношения производительности на ватт и значительного снижения задержек для рабочих нагрузок CPU, в том числе для контроллера памяти (IMC).