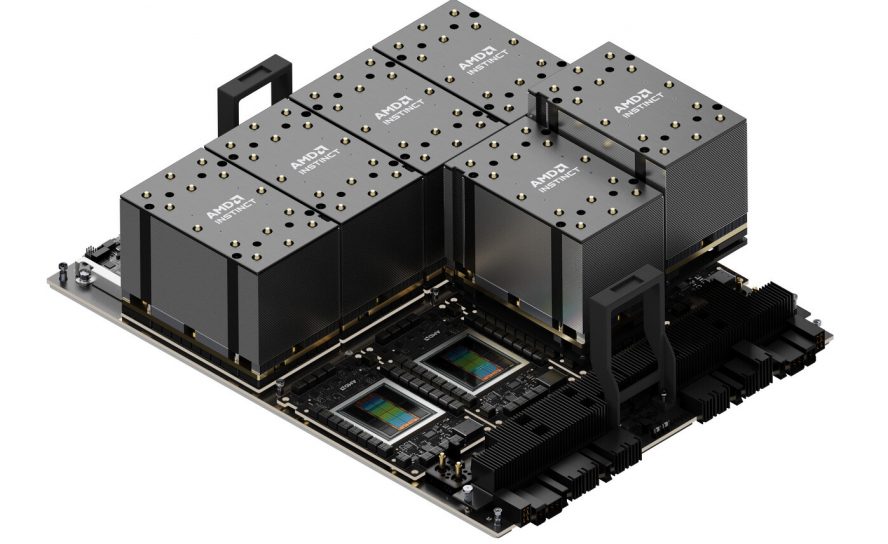

Ускорители AMD Instinct MI400, выход которых запланирован на 2026 год, будут включать новый выделенный чип для мультимедийного ввода-вывода (MID) наряду с существенным увеличением вычислительной плотности. Согласно последним патчам, обнаруженным в списках рассылки AMD-GFX, ускоритель будет иметь двойную конструкцию с активными интерпозерами (AID), каждый из которых будет содержать четыре вычислительных чипа (XCD). Это вдвое больше, чем в текущей серии MI300.

Внедрение выделенных чипов MID — это новый этап в философии проектирования ускорителей AMD. Документация указывает на поддержку до двух MID, каждый из которых, вероятно, будет связан с одним AID, что говорит о более специализированном подходе к обработке мультимедиа и управлению интерфейсами.

Спецификации, полученные из реализации таблицы переназначения регистров (RRMT), указывают на сложные пути связи между чипами с поддержкой локальных и удаленных транзакций между XCD, AID и новыми MID. Система обеспечивает детальный контроль над восемью возможными конфигурациями XCD (от XCD0 до XCD7), предполагая, что AMD сможет масштабировать вычислительные ресурсы в зависимости от модели ускорителя.

Хотя AMD еще не опубликовала подробные характеристики серии MI400, выделение мультимедийных функций в отдельные чипы может оптимизировать производительность и энергоэффективность. По мере приближения запуска в 2026 году AMD будет уделять оставшееся время доработке программного стека и поддержке ROCm для своих ускорителей следующего поколения на базе архитектуры UDNA. Учитывая, что проектирование ускорителя с точки зрения физической реализации занимает около года, можно предположить, что разработка Instinct MI400 уже завершена. Остаются этапы запуска кремния, оптимизации программного обеспечения и массового производства, которое, вероятно, будет осуществляться на мощностях TSMC.