В мире, где требования к производительности искусственного интеллекта и дата-центров растут экспоненциально, привычные методы усовершенствования чипов, известные как Закон Мура, уже не справляются. Мы оказались перед критическим барьером: как уместить больше вычислительной мощи в меньшем пространстве, не превратив ее в печку?

Ответ, кажется, найден в третьем измерении. Глобальный лидер в области высокоскоростных соединений, компания Alphawave Semi, объявила об успешном завершении ключевого этапа разработки своего передового 3D-интерфейса UCIe с использованием революционной технологии SoIC-X от производственного гиганта TSMC. Этот успех знаменует собой значительный шаг вперед в архитектуре будущих чипов.

Преодоление границ кремния

Традиционно чипы общаются друг с другом только по периметру, что похоже на попытку пропустить весь трафик мегаполиса через одну узкую кольцевую дорогу. Когда модели ИИ становятся все более сложными, этот «береговой» метод связи начинает серьезно ограничивать скорость передачи данных и функциональность, которую можно вместить в один корпус.

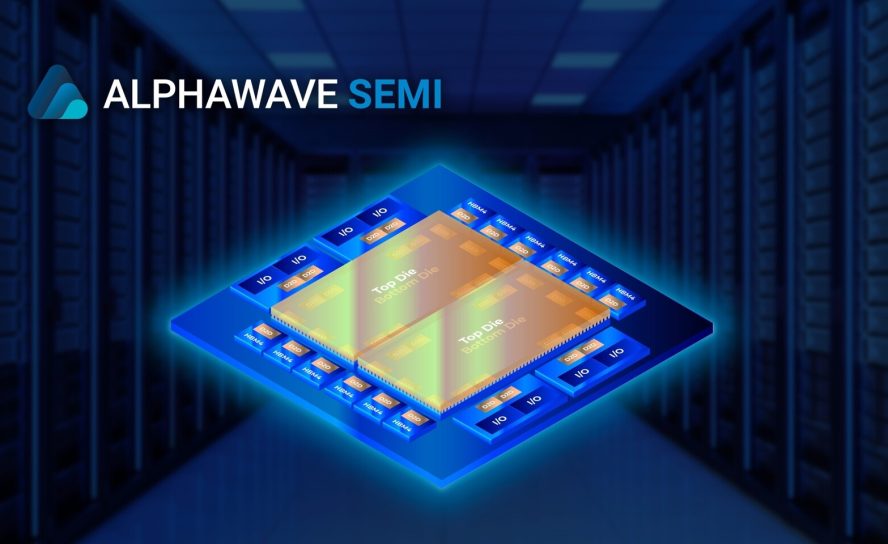

Чтобы преодолеть это, инженеры переходят от классических монолитных процессоров к дезагрегированным архитектурам, где отдельные функциональные блоки (чиплеты) собираются вместе. Самый эффективный путь — вертикальная сборка, или 3D-стекирование.

Именно здесь на сцену выходит разработка Alphawave Semi. Используя технологию TSMC SoIC-X (часть платформы 3DFabric), компания добилась впечатляющих результатов. Новый 3D-интерфейс, который поддерживает конфигурацию «лицом к лицу» (Face-to-Face, F2F), обеспечивает десятикратное улучшение энергоэффективности по сравнению с традиционными двумерными интерфейсами и позволяет увеличить плотность сигнала до пяти раз.

Проще говоря, это означает, что чипы смогут обмениваться данными не только быстрее, но и потреблять при этом гораздо меньше энергии, что критически важно для масштабных центров обработки данных и суперкомпьютеров.

Слияние инноваций

В этой 3D-архитектуре нижний чип, выполненный по 5-нм техпроцессу, использует микроскопические сквозные соединения (TSV) для питания и заземления верхнего чипа, изготовленного по новейшему 3-нм стандарту. Для ускорения внедрения этой сложной технологии, Alphawave Semi также разработала собственную методологию проектирования для быстрой и надежной проверки всей трехмерной конструкции.

Мохит Гупта, исполнительный вице-президент Alphawave Semi, подчеркнул: «Успешный «tape-out» (завершение дизайна) — это важная веха для нашей платформы искусственного интеллекта. Объединяя наш высокоскоростной 3D UCIe IP с новаторской технологией SoIC-X от TSMC, мы напрямую решаем проблемы пропускной способности и памяти, которые сдерживают развитие ИИ следующего поколения».

Этот прорыв является результатом тесного сотрудничества с партнерами по экосистеме. Представители TSMC и Siemens (чей продукт Calibre используется для проектирования 3D-чипов) подтвердили, что партнерство с Alphawave Semi имеет решающее значение для того, чтобы их общие клиенты могли в полной мере использовать все преимущества передовых технологий 3DFabric и 3D-стекирования для повышения энергоэффективности и производительности в системах искусственного интеллекта.

Новость о 3D-прорыве последовала за июньским объявлением Alphawave Semi о разработке своего интерфейса UCIe с использованием 2-нм процесса TSMC и 2.5D-технологии CoWoS. Компания продолжает активно работать над следующими поколениями решений UCIe, поддерживающими скорость 64G, и уверенно движется к будущему, управляемому архитектурой чиплетов.