AMD в ходе сессии вопросов и ответов с прессой, посвященной архитектуре, подтвердила, что ядра «Zen 5» и «Zen 5c» в кремнии «Strix Point» имеют только 256-битные FPU, в отличие от ядер «Zen 5» в настольных процессорах «Granite Ridge» Ryzen 9000. «Zen 5c, используемый в Strix, имеет 256-битную шину данных, и то же самое относится к Zen 5, используемому в Strix», — сказал Майк Кларк, корпоративный стипендиат AMD и главный архитектор ядер «Zen».

«Таким образом, нет никакой разницы, когда вы переходите [миграция потоков между комплексами Zen 5 и Zen 5c] в векторной пропускной способности», — добавил он. Похоже, что AMD не отключала физически доступную функцию, а вместо этого разработала вариант ядер «Zen 5» и «Zen 5c», которые физически лишены 512-битной шины данных. «И вы получаете преимущество в площади, чтобы иметь возможность немного больше масштабироваться», — продолжил Кларк.

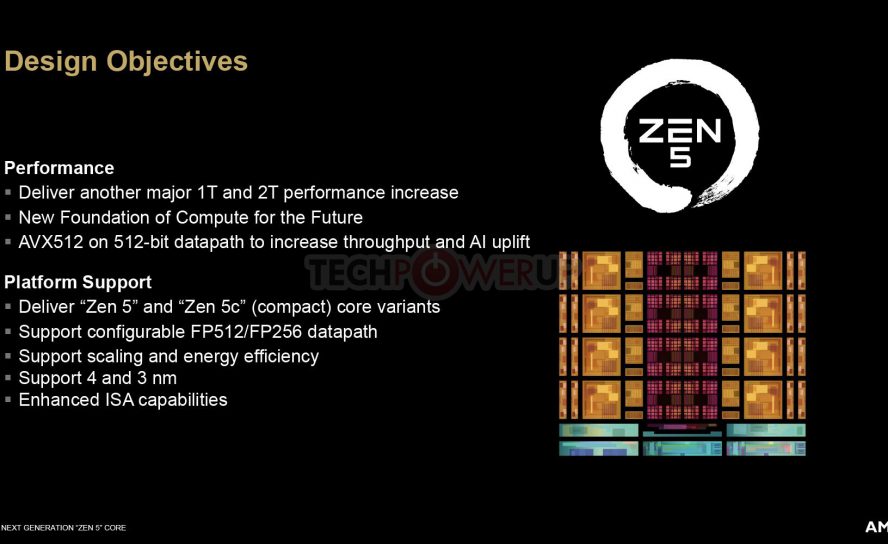

Это говорит о том, что ядра «Zen 5» и «Zen 5c» в «Strix Point» физически меньше, чем те, которые используются в 4-нанометровом 8-ядерном CCD «Eldora», который присутствует в «Granite Ridge» и некоторых ключевых моделях предстоящих серверных процессоров EPYC 5-го поколения «Turin». Одним из главных достоинств микроархитектуры «Zen 5» является ее блок с плавающей запятой, который поддерживает AVX512 с полной 512-битной шиной данных. Для сравнения, «Zen 4» предыдущего поколения обрабатывал AVX512 с использованием 256-битного FPU с двойной пропускной способностью. Новый 512-битный FPU, в зависимости от конкретной нагрузки и других факторов, примерно на 20-40% быстрее, чем «Zen 4» при работе с 512-битными вычислениями с плавающей запятой.

Именно поэтому от «Zen 5» ожидается значительный прирост производительности в задачах AI-вывода, а также в бенчмарках, использующих AVX512. Нам не ясно, как отсутствие 512-битного FPU влияет на производительность инструкций, связанных с ускорением AI, так как «Strix Point» в основном предназначена для AI-компьютеров с поддержкой Microsoft Copilot+. Возможно, AVX512 и AVX-VNNI выполняются на 256-битной шине данных с двойной пропускной способностью, подобно тому, как это делается в «Zen 4». Это решение может быть выгодным с точки зрения производительности/ватт, что актуально для мобильных платформ.

Самое важное:

* Ядра «Zen 5» и «Zen 5c» в SoC «Strix Point» имеют 256-битные FPU, в отличие от ядер «Zen 5» в настольных процессорах «Granite Ridge» Ryzen 9000, где используются 512-битные FPU.

* AMD не отключает физически доступную функцию, а вместо этого разработала варианты ядер «Zen 5» и «Zen 5c» с 256-битными FPU.

* Это решение позволяет AMD уменьшить размер ядер, что важно для мобильных платформ.

* «Zen 5» в «Granite Ridge» отличается 512-битным FPU, что позволяет ему работать с AVX512 с максимальной эффективностью, повышая производительность в 20-40% по сравнению с «Zen 4» при работе с 512-битными вычислениями с плавающей запятой.

* Неясно, как отсутствие 512-битного FPU в «Strix Point» влияет на производительность при ускоренных вычислениях AI, так как эта платформа ориентирована на AI-компьютеры с поддержкой Microsoft Copilot+.

* Возможно, AVX512 и AVX-VNNI в «Strix Point» работают на 256-битной FPU с двойной пропускной способностью, как в «Zen 4».

* Это решение может быть выгодным с точки зрения производительности/ватт, что актуально для мобильных платформ.