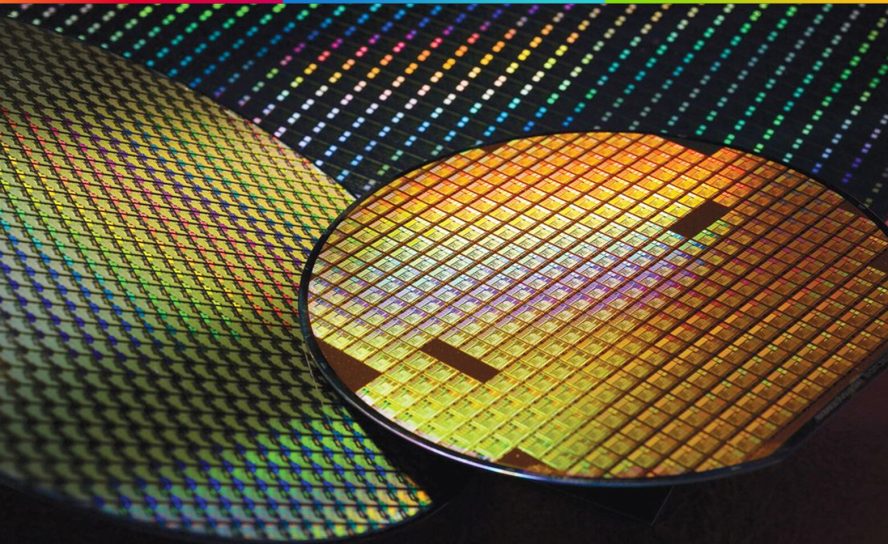

Компании Cadence и TSMC объявили о крупном прорыве в сфере автоматизации проектирования чипов (EDA) и развитии IP-блоков. Благодаря многолетнему партнерству, Cadence активно работает над передовой инфраструктурой проектирования, чтобы максимально ускорить вывод на рынок новых чипов для ИИ и высокопроизводительных вычислений (HPC).

Сотрудничество между Cadence и TSMC охватывает весь спектр технологий: от ИИ-управляемого EDA и 3D-интегральных схем (3D-IC) до фотоники и IP-блоков. Совместные усилия привели к созданию комплексной инфраструктуры для самых передовых норм, включая TSMC N3, N2 и даже будущий A16. Все ключевые инструменты Cadence, включая Innovus, Quantus, Tempus, Pegasus и Spectre, теперь оптимизированы для этих узлов.

Впервые Cadence представила полные ИИ-управляемые потоки проектирования чипов и 3D-IC для передовых технологий TSMC N3, N2 и A16, а также для новых функций платформы TSMC 3DFabric. Более того, Cadence уже работает над потоками EDA для техпроцесса TSMC A14, первый пакет проектирования (PDK) которого ожидается позднее в этом году.

Особое внимание уделяется повышению эффективности проектирования с помощью искусственного интеллекта. TSMC валидировала ИИ-управляемую технологию реализации Cadence Cerebrus Intelligent Chip Explorer, которая, совместно с Cadence JedAI Solution, позволяет клиентам достигать оптимальных показателей мощности, производительности и площади (PPA) на норме TSMC N2. В число новых ИИ-функций также вошла автоматизированная помощь в исправлении ошибок проверки проектных правил (DRC), что ускоряет завершение проектов ИИ-чипов.

Решения для 3D-IC и флагманские IP-блоки

Для систем с многокристальной компоновкой Cadence предоставила комплексную поддержку расширенной упаковки TSMC 3DFabric, включающую автоматизацию соединений, физическую реализацию и анализ нескольких чиплетов. Технологии Clarity 3D Solver и Sigrity X Platform теперь используют ИИ для автоматизации SI/PI анализа и оптимизации системного уровня на базе 3Dblox.

В сфере IP-блоков Cadence продолжает демонстрировать лидерство, выпуская кремниево-проверенные решения для TSMC N3P. Эти IP-блоки призваны решить проблему «барьера памяти», которая ограничивает современные ИИ-системы. Среди новинок на N3P — первый IP для памяти HBM4, высокоскоростные интерфейсы LPDDR6/5X (14.4G) и универсальный DDR5 12.8G MRDIMM Gen 2. В области подключений Cadence лидирует с IP для PCI Express (PCIe) 7.0, обеспечивающим скорость 128 ГТ/с, и первым IP для UCIe 32G, который необходим для развивающихся экосистем ИИ-ПК и чиплетов.

По словам Чин-Чи Тенга, старшего вице-президента Cadence, этот альянс нацелен на ускорение и улучшение процесса проектирования, чтобы помочь разработчикам создавать следующее поколение систем ИИ и HPC.