Гонка в сфере искусственного интеллекта продолжает набирать обороты. Похоже, что NVIDIA и AMD готовят настоящий прорыв в архитектуре своих будущих ускорителей. Как сообщает аналитическое агентство SemiAnalysis, компании впервые в истории перейдут на использование кастомизированной памяти HBM4, чтобы получить серьёзное преимущество над конкурентами.

Обычно в стеке памяти HBM используется стандартная компоновка: несколько чипов DRAM, соединенных между собой через сквозные кремниевые перемычки (TSV). Однако в нижней части такого стека всегда есть место для дополнительной логической микросхемы. Именно эту возможность NVIDIA и AMD собираются использовать, чтобы интегрировать в свои ускорители специально разработанные базовые чипы. Эти чипы, по всей видимости, будут содержать специализированную логику, заточенную под конкретные задачи.

По мнению экспертов, такой подход позволит обоим гигантам опередить сторонних разработчиков специализированных решений для ИИ, так называемых ASIC, примерно на треть. Причина проста: в то время как другие компании, например Broadcom и MediaTek, смогут внедрить подобные кастомизированные чипы только к 2027 году, NVIDIA и AMD планируют использовать их уже в своих продуктах 2026 года.

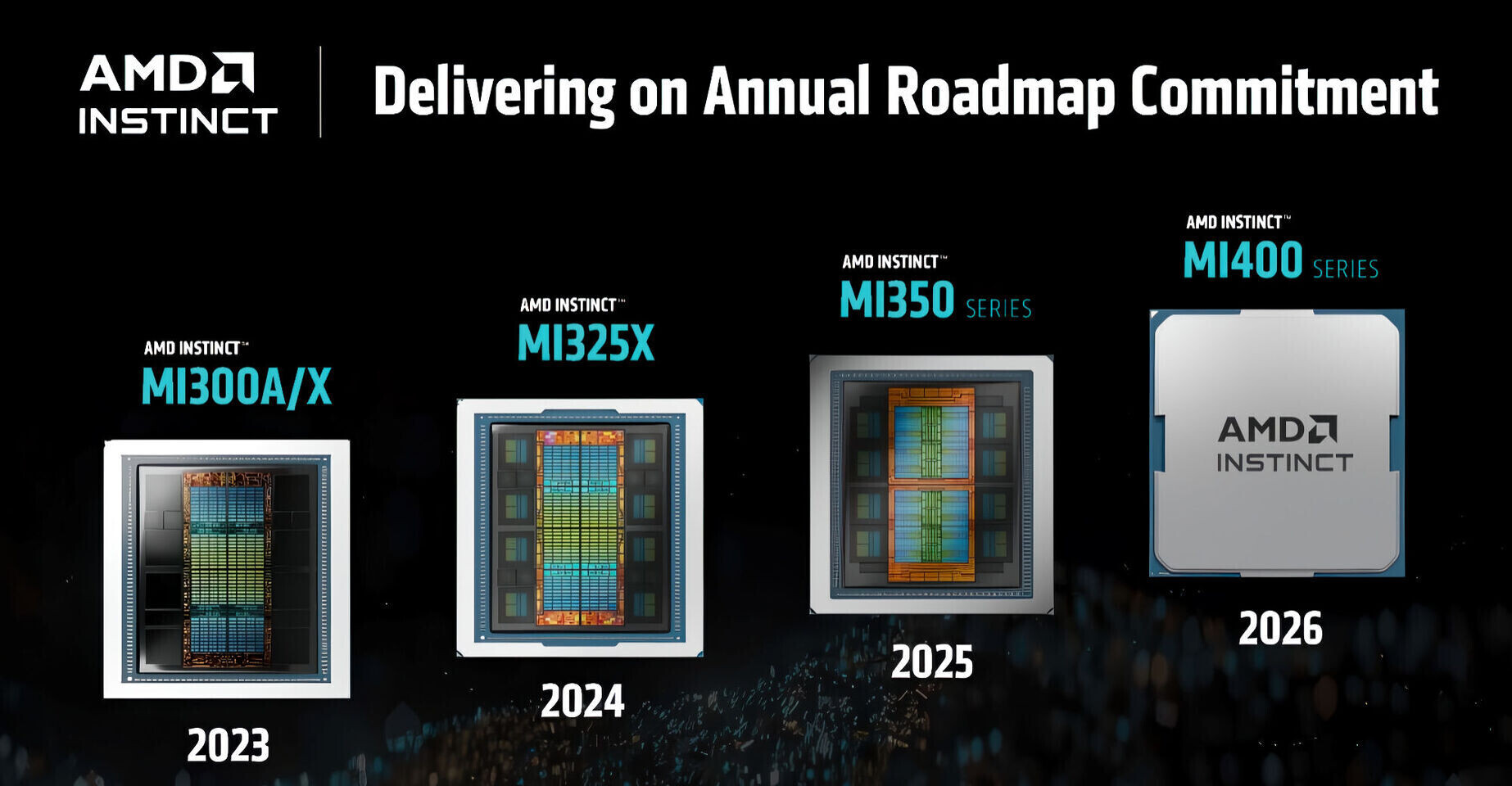

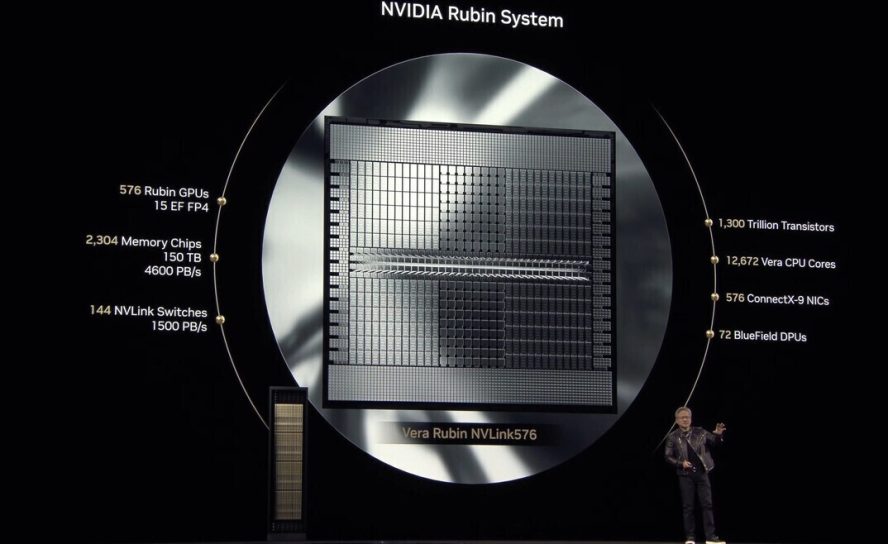

Для NVIDIA это будет архитектура «Rubin», которая, как ожидается, значительно превзойдёт текущее поколение «Blackwell». AMD же применит эту технологию в своей серии ускорителей Instinct MI400, которые впервые выйдут в форм-факторе для серверных стоек.

Обычно производители используют стандартную HBM-память, поскольку это позволяет им рассчитывать на предсказуемую стоимость от таких поставщиков, как Samsung, Micron и SK Hynix. Однако NVIDIA и AMD, заказывая колоссальные объёмы, могут диктовать свои условия и требовать особых доработок. Вместо того, чтобы просто увеличить вычислительную мощность, эти кастомные базовые чипы, скорее всего, будут выполнять функции более эффективной маршрутизации данных. Это позволит снизить задержки и значительно повысить пропускную способность, особенно при инференсе — этапе, где каждая миллисекунда на счету. Подобное «умное» управление памятью может обеспечить двузначный прирост производительности.